We have all experienced it: when purchasing Apple phones, the price varies greatly with different memory sizes. This memory refers to flash memory (Flash), and Apple was the first company to use flash memory to store data. Flash memory includes two types: NOR Flash and NAND Flash. However, NOR Flash has a smaller capacity, generally ranging from 1Mb to 2Gb, while NAND Flash can provide a very high cell density, achieving high storage density, suitable for the storage of a large amount of data, and is also the mainstream flash memory technology. Since 2018, most smartphones worldwide have started using 3D NAND storage chips. It's not just smartphones; 3D NAND chips are also very popular in data centers, the cloud, servers, SSDs, PCs, and other fields.

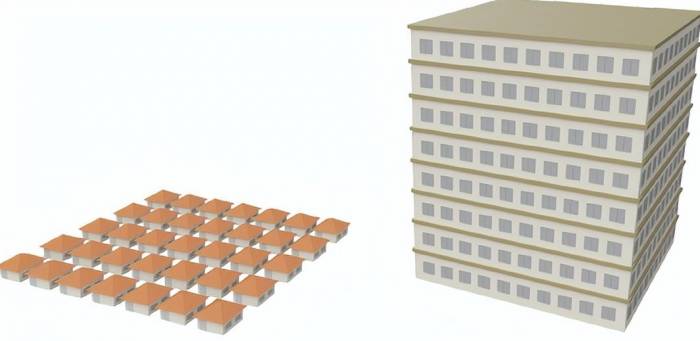

Before the introduction of 3D NAND technology, NAND flash memory was all in a 2D planar form. The principle of the 2D NAND architecture is like building houses on a limited flat surface; the more houses, the greater the capacity. In the past, storage chip manufacturers expanded the cell size in the planar NAND from 120nm to the 1xnm node, achieving a 100-fold increase in capacity. However, as the cell size reaches the physical limit of 14 nanometers, the 2D structure has significant limitations in expanding storage capacity (once the process size reaches a certain stage, flash memory is prone to losing the data stored due to electron loss).

As the miniaturization of 2D NAND reaches its limit, in 2007, Toshiba (now Kioxia) proposed the technical concept of 3D NAND structure, which is an innovative direction for the industry. Unlike planar NAND that reduces the cell size at each node, 3D NAND uses a more relaxed process, roughly between 30 nanometers and 50 nanometers, and achieves greater storage capacity by increasing the number of vertical layers. Therefore, we can also see that the current mainstream storage chip manufacturers are competing to increase the vertical gate count of 3D NAND to improve storage density. They have planned the next generation of 3D NAND products, including 232 layers/238 layers, and even larger to 4xx layers or even 8xx layers. Although they are all building buildings, the architecture used by each company is different.

Architecture 1: V-NAND, Representative Manufacturer: Samsung

In 2013, Samsung took the lead in launching V-NAND flash memory, where V stands for Vertical, meaning vertical. This is a solution that connects its cell layers through vertical stacking in 3D space. Samsung is the world's first company to develop and commercialize 3D memory solutions, creating a new paradigm for the storage industry.

In 2013, the first V-NAND flash memory developed by Samsung had only 24 layers. Currently, Samsung's V-NAND has developed to the eighth generation, with more than 200 layers. On November 7, 2022, Samsung announced that it has started mass production of the eighth-generation 1TB 3D NAND (V-NAND) with more than 200 layers and plans to promote it to the market according to consumer demand. Moreover, Samsung's goal is to achieve 1000 layers by 2030. V-NAND flash memory has been continuously developing, with each new generation of V-NAND bringing significant performance improvements and lower power consumption.

It is worth mentioning that before the V-NAND 128 layers, Samsung's V-NAND used a single-layer etching technology, connecting the battery through cylindrical channels, capable of stacking more than 100 layers at a time, and interconnecting through more than 1 billion holes. In addition to its innovative structure, V-NAND also uses Charge Trap Flash (CTF) technology to eliminate interference between cells. By introducing a non-conductive silicon nitride layer in the battery, CTF technology makes V-NAND technology immune to charge leakage and data damage. With the support of this ultra-high aspect ratio (UHAR) hole etching single-layer technology, Samsung has been leading the 128-layer 3D NAND.

However, single etching can only reach up to 128 layers, so beyond the 128-layer devices, many competitors use a double-layer method, such as Micron stacking two 88-layer structures to form a 176-layer device; Intel's 144L 3D QLC design has turned to a 3-layer stack: 48 + 48 + 48 layers, which is easier to implement. The fewer the layers, the easier it is to perform the HAR etching steps.By the seventh generation of 512Gb 176-layer TLC chips, Samsung began to adopt the COP (Cell-on-Periphery) structure, and the subsequent 1Tb 238L TLC products will be the second-generation COP TCAT V8 V-NAND. The storage cell array area of the COP structure is located above the peripheral devices, but there are still some peripheral devices outside the cell array in the COP structure, which means that the cell array and the peripheral area below and next to the cell array must be reduced to decrease the chip size.

Architecture II: CuA, representing manufacturers: Micron/Intel

Micron has been using this method of building its 3D NAND array on the peripheral logic of the chip since the first generation of 32-layer 3D NAND. Micron calls it CuA (CMOS-under-array). This architecture provides an expansion method for capacity growth, density, performance, and cost improvement. By stacking the NAND bit cell array into more layers, it provides more bits per square millimeter of silicon wafer, thus achieving higher density and lower cost per bit.

In late July 2022, Micron announced its 232-layer 3D NAND, which, according to Micron, achieves the highest TLC density per square millimeter (14.6 Gb/mm2). The areal density is 35% to 100% higher than that of similar TLC products. According to Micron's information, this 3D NAND device is divided into six planes (many NAND devices on the market today only have two planes, and some cutting-edge designs use four plane partitions to channel commands and data streams) to achieve higher parallelism, thereby improving performance. On the basis of each chip, the increased parallelism improves the sequential and random access read and write performance by supporting more read and write commands that can be issued to the NAND device simultaneously. Just like a highway, the more lanes there are, the less congestion, and the greater the traffic flow through a given area. Micron's 232-layer NAND is now shipping.

Intel and Micron previously developed FG CuA 3D NAND. Here's a brief introduction: NAND flash memory storage cell technology is roughly divided into floating gate (FG) technology and charge trap (CT) technology. The FG technology storage cell has a gate (floating gate) that is electrically floating between the control gate and the channel of the cell transistor, and data is written by injecting charge into the floating gate (changing the threshold of the cell transistor).

The mainstream technology used in previous 2D NAND flash memory was FG technology. However, as NAND flash memory technology moved from 2D to 3D, all major manufacturers except the Intel-Micron alliance abandoned FG technology in favor of CT technology, as mentioned in the above text, such as Samsung. The main reason for adopting CT technology is that it is simpler to manufacture through-hole memory devices than FG technology. FG technology is highly regarded for its excellent data retention characteristics, high-temperature characteristics, and superior controllability compared to CT technology.There are three generations of 3D NAND flash technology developed by the Intel-Micron Alliance. The first generation is a silicon die that combines 32 layers of memory vias and TLC (3bit/cell) type multi-level memory, with a memory capacity of 384Gbit. The second generation fully introduced CuA technology, doubling the number of layers to 64 layers (2 32-layer stacks) of silicon chips, and combined with TLC and QLC (4 bit/cell) multi-level memory technology to achieve commercialization. The third generation reached 96 layers (2 48-layer stacks), with the same storage capacity as the second generation, and the silicon area was reduced to about 76%. Intel's fourth-generation 144-layer turned to self-development. For the first time, this NAND string consists of three layers (upper deck, middle deck, lower deck and 48L) between source and bitline, and retains the FG CuA structure for TLC and QLC devices. Each deck can be assigned to any combination of QLC or SLC blocks to fully benefit from Intel's new block-by-deck concept in storage systems. However, Intel has withdrawn from the 3D NAND market and sold the business to SK Hynix for $9 billion. Architecture 3: BiCS, representative manufacturers: Kioxia/WD/SK Hynix Kioxia and Western Digital (WD) are jointly developing 3D NAND called BiCS Flash. Kioxia's predecessor was Toshiba. As mentioned at the beginning, Toshiba was the first company in the world to invent flash memory (1987) and propose 3D NAND technology. As early as when Kioxia was Toshiba, it established a flash memory partnership with SanDisk. Later, Western Digital acquired SanDisk, Toshiba became Kioxia, and the two established a joint venture Flash Ventures (FV) and became partners. FV is owned 50/50 by WD/Kioxia, and the wafer production capacity is also divided into 50/50 shares. KIOXIA proposed the concept of BiCS FLASH “batch processing technology” at an academic conference in 2007. According to Kioxia's explanation of BiCS FLASH™'s "batch technology", in BiCS FLASH™, there is a plate electrode as a control gate (green plate in the figure below) and an insulator are alternately stacked, and then a large number of holes are opened (punched) perpendicular to the surface at the same time. Next, the inner part of the hole opened in the plate electrode is filled (blocked) with a charge storage film (pink part) and a columnar electrode (gray part is a columnar structure). Under this condition, the intersection of the plate electrode and the columnar electrode is a storage unit. In the BiCS FLASH™ storage unit, electrons are exchanged between the electrode (gray structure) passing through the center of the column and the charge storage film (pink). In this way, the storage units are not stacked layer by layer, but the plate electrodes are stacked first, and then a hole is opened between them to connect the electrodes, so that all layers of storage units are formed at one time to reduce manufacturing costs. In 2015, Kioxia & Western Digital launched 48-layer BiCS 3D NAND, 64-layer in 2017, 96-layer in 2018, and 112-layer in 2020. In 2021, Kioxia and Western Digital announced their sixth-generation BiCS 3D NAND technology, which has 162 layers, and is also the first product using the CuA concept. The roadmap revealed by Western Digital shows that the next generation "BiCS+" will be launched at the end of 2023, and the number of layers should increase to more than 200. As one of the world's leading NAND flash companies, SK Hynix is the last company to develop 3D NAND flash technology. According to Tech insights, from 2015 to 2019, SK Hynix successively developed four types of memory cell arrays: the first memory cell array developed from 2015 to 2016 adopted a structure similar to the cell array "P-BiCS" developed by Kioxia called "SP-BiCS", which seemed to be 32 layers; in 2017, it developed an improved version of the memory cell array-"DP-BiCS Gen1", which is estimated to be 48 layers; in 2018, SK Hynix developed a memory cell array called "DP-BiCS Gen2", which has a structure that divides the memory stack into two "layers" (also called "decks"), estimated to be 72 layers.Architecture Four: 4D PUC, Representative Manufacturer: SK Hynix

In November 2018, starting from the fourth-generation 96-layer 3D NAND, SK Hynix introduced a new naming method—4D PUC (Periphery Under Cell). PUC is a technology that repositions peripheral circuits to the bottom of the cell, as shown in the figure below. Despite the name, the company did not create products in four-dimensional space. The number "4" actually represents a level of advancement (rather than entering the fourth dimension). It is a commercial name for a variant of the 3D architecture. The first so-called 4D NAND devices improved the peripheral circuits under the CTF (Charge Trap Flash) NAND array, thus saving more space on the chip and further reducing production costs. According to SK Hynix, compared to 3D, the 4D product has a smaller unit area and higher production efficiency.

After 98 layers, SK Hynix has successively developed 128-layer and 176-layer 3D NAND. In August 2022, SK Hynix announced that it has developed the world's highest 238-layer 4D NAND flash memory, which is also the smallest NAND in size, and is expected to start mass production in the first half of 2023. SK Hynix's current 4D NAND technology is now recognized as an industry standard.

The PUC architecture allows 4D NAND to achieve high density in a fixed area, reducing the chip size. However, the disadvantage is that the stacking technology may reach its limit in the future. SK Hynix plans to overcome this obstacle with Multi-Stack Cell (MSC) as the core, reducing the number of cell stacks by dividing the existing cells into two smaller cells for data storage through micro-manufacturing, while horizontally expanding cell density. This is also one of the core elements of SK Hynix's 4D 2.0 technical concept.

Architecture Five: Xtacking, Representative Manufacturer: Yangtze Memory Technologies

In addition to the storage array in 3D flash memory, these peripheral circuits occupy a considerable area of the chip. It can be seen that most of the architectures adopted by the aforementioned storage manufacturers are to place the peripheral circuits under the storage unit. However, Yangtze Memory Technologies adopts a completely different method from other companies—Xtacking.

Xtacking technology separates the storage array and peripheral circuits, processing them on two independent wafers. Although NAND flash memory is not suitable for processing with more advanced processes, the peripheral circuits can be. After the two parts are completed using the appropriate process nodes, the completed memory array wafer is connected to the peripheral wafer through tens of billions of vertical interconnects (VIAs). As shown in the figure below, the peripheral circuits are located above the memory, and then they are stacked and connected through copper hybrid bonding technology to achieve higher bit density. However, this bonding technology is still very expensive.Translation:

Summary

So far, the mainstream 3D NAND architectures are roughly these five types: V-NAND, BiCS, CuA (COP), 4D PUC, and Xtacking. However, just like building a high-rise building, simply stacking layers is not the ultimate goal. A high-rise building must not only be tall but also ensure that it can be easily reached through safe and efficient elevators, that is, whether the V-NAND inside each storage chip can continue to rise in a faster, more efficient, and more power-saving way? This is a great test of each company's capabilities. With the advancement of NAND technology, limitations will also emerge.